-

- Sopto Home

-

- Special Topic

-

- PCI-E Card Knowledge

-

- How PCIe Reduces Bandwidth Efficiency?

PCI-E Card Knowledge

- Info about Network Interface Card Teaming

- How to Setup a Server with Multiple Network Interface Adapters?

- How to Reconnect an Internet Network Adapter for an Acer Aspire?

- 9 Things to Do When Your Internal Network Card Stops Working

- Ethernet Standards NIC for Home Networking

- What Is a Network Interface Adapter?

- How to Configure a Network Interface Card in Linux?

- How should Configure Your NIC for ISA and TMG?

- Recommended Network Card Configuration for Forefront UAG Servers

SOPTO Special Topic

Certificate

Guarantee

Except products belongs to Bargain Shop section, all products are warranted by SOPTO only to purchasers for resale or for use in business or original equipment manufacturer, against defects in workmanship or materials under normal use (consumables, normal tear and wear excluded) for one year after date of purchase from SOPTO, unless otherwise stated...

Return Policies

Defective products will be accepted for exchange, at our discretion, within 14 days from receipt. Buyer might be requested to return the defective products to SOPTO for verification or authorized service location, as SOPTO designated, shipping costs prepaid. .....

Applications

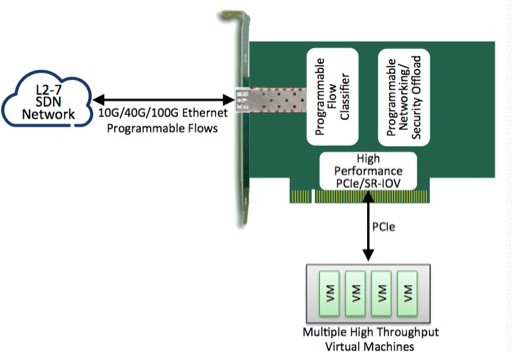

PCI-E NIC Cards provide redundant connectivity to ensure an uninterrupted network connection.

PCI-E NIC Cards are ideal for VM environments with multiple operating systems, requiring shared or dedicated NICs.

They are specially designed for desktop PC clients, servers, and workstations with few PCI Express slots available.

SOPTO Products

- Fiber Optic Transceiver Module

- High Speed Cable

- Fiber Optical Cable

- Fiber Optical Patch Cords

- Splitter CWDM DWDM

- PON Solution

- FTTH Box ODF Closure

- PCI-E Network Card

- Network Cables

- Fiber Optical Adapter

- Fiber Optical Attenuator

- Fiber Media Converter

- PDH Multiplexers

- Protocol Converter

- Digital Video Multiplexer

- Fiber Optical Tools

- Compatible

Related Products

Performance Feature

PCI-E Card Knowledge

Recommended

How PCIe Reduces Bandwidth Efficiency?

While the PCI Express standard is impressive in that it actually makes sense (well, most of the time) there is a pretty annoying thing about read requests reordering.

The TLP packet formation is that read requests may be reordered as they travel across the switching network, and same goes for read completions associated with different read requests. The read-related packets, which must arrive in the same order they were sent, are read completions associated with the same read request, or as the spec puts it: “… must return in address order”.

This would be a good time to mention, that a read request may be larger than the maximal payload size, so obviously the completer must have a means of splitting the completion into several TLPs, which must be sent in rising address order. And if we’re at it, there’s a boundary restriction on how to cut the data in pieces, namely that the cuts are on boundaries of RCB, where RCB can either be 64 bytes or 128 bytes (if you’re not a Root Complex you may cut on 128-byte boundaries only, and if you are a Root Complex, you choose 64 or 128, and configure the endpoints telling then what you chose).

And there’s a restriction on the maximal read request size, but that’s a different story.

So far the specification makes sense: Read completions will be split into several TLPs pretty often, and they have to arrive to the requester in linear address order, so these packets must not be reordered.

But what if the endpoint needs to collect a chunk of data which is larger than the maximal read request size (typically 512 bytes)? It will have to issue several read requests for that. But read requests and completions from different read requests may be reordered.

So if we want to assure that the data arrives in linear order (which is necessary when the data goes into a FIFO-like data sink) each read request can be transmitted only when the last completion TLP from the previous request arrives. Otherwise, a completion TLP from the following request may arrive before that last packet. Hence there’s a time gap of non-utilized bandwidth.

In general there is no problem having several outstanding read requests. So had read requests and read completions been strictly ordered, it would be possible to send the following read request more or less immediately after the first one, and completions would arrive continuously.

Another issue, which is less likely to bother anyone, is that if some software makes assumptions on the order at which data in some buffer is updated, this can cause rare bugs.

For example, if the read completions update some dual port RAM, and there’s software reading from this buffer, it may deduce from the update of some high-addressed memory cell that the entire buffer is updated.

For the newest quotes of PCI Express Server Cards, please contact a Sopto representative by calling 86-755-36946668, or by sending an email to info@sopto.com.