-

- Sopto Home

-

- Special Topic

-

- PCI-E Card Knowledge

-

- Altera’s IP compiler for PCI express, and how to survive it?

PCI-E Card Knowledge

- Info about Network Interface Card Teaming

- How to Setup a Server with Multiple Network Interface Adapters?

- How to Reconnect an Internet Network Adapter for an Acer Aspire?

- 9 Things to Do When Your Internal Network Card Stops Working

- Ethernet Standards NIC for Home Networking

- What Is a Network Interface Adapter?

- How to Configure a Network Interface Card in Linux?

- How should Configure Your NIC for ISA and TMG?

- Recommended Network Card Configuration for Forefront UAG Servers

SOPTO Special Topic

Certificate

Guarantee

Except products belongs to Bargain Shop section, all products are warranted by SOPTO only to purchasers for resale or for use in business or original equipment manufacturer, against defects in workmanship or materials under normal use (consumables, normal tear and wear excluded) for one year after date of purchase from SOPTO, unless otherwise stated...

Return Policies

Defective products will be accepted for exchange, at our discretion, within 14 days from receipt. Buyer might be requested to return the defective products to SOPTO for verification or authorized service location, as SOPTO designated, shipping costs prepaid. .....

Applications

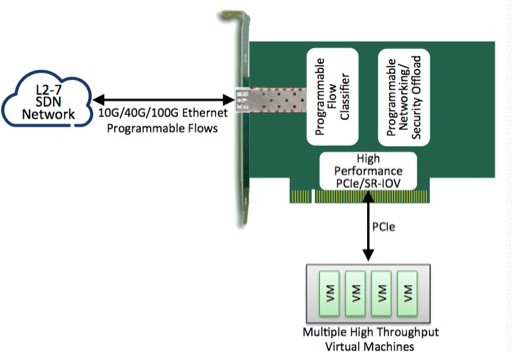

PCI-E NIC Cards provide redundant connectivity to ensure an uninterrupted network connection.

PCI-E NIC Cards are ideal for VM environments with multiple operating systems, requiring shared or dedicated NICs.

They are specially designed for desktop PC clients, servers, and workstations with few PCI Express slots available.

SOPTO Products

- Fiber Optic Transceiver Module

- High Speed Cable

- Fiber Optical Cable

- Fiber Optical Patch Cords

- Splitter CWDM DWDM

- PON Solution

- FTTH Box ODF Closure

- PCI-E Network Card

- Network Cables

- Fiber Optical Adapter

- Fiber Optical Attenuator

- Fiber Media Converter

- PDH Multiplexers

- Protocol Converter

- Digital Video Multiplexer

- Fiber Optical Tools

- Compatible

Related Products

Performance Feature

PCI-E Card Knowledge

Recommended

Altera’s IP compiler for PCI express, and how to survive it?

Xillybus is now supporting Altera FPGAs having the hard IP transceiver for PCI Express (and other Gigabit interfaces). If you’re into PCI Express, and into a fairly recent project, odds are that your device is on the list.

There is, of course, the possibility to handle the Avalon-ST interface by yourself, with its quirky Endianess issues. The payload is Endian swapped, the header isn’t.

Or its “interesting” alignment of DWords in QWords, making it Avalon compatible, but also opens an opportunity for exotic bugs in getting the payload data right. And is it only me not being very fond of the delay of three clock cycles between deasserting rx_st_ready and rx_st_valid going low? That kind-of forced me to put a FIFO in between.

When I can’t get more data, I can’t. Period. And just to play completely unfair, the application logic may deassert tx_st_valid, but not in the middle of a TLP. So much for flow control.

They call it ready Latency, but I call it practically no flow control. This is not to say that the Altera’s PCIe core is bad. It just has its little corners. As has PCI Express itself: Minding the credits for incoming read request completions is something one can’t get away from: In theory, it should have been the data link layer’s work, but since it’s forced to announce infinite credits on completions to unposted requests, user logic must make sure the completion buffers don’t overflow.

Having the user logic aware of max_payload_size and the maximal read request size is just another little detail to handle.

Gigabit Dual RJ45 Slots 1.0 PCI-E Server Adapter Card

Not to mention the need to know our bus and device number (the function is always zero. Shhh.). The chosen implementation for retrieving this information (a.k.a. the “Configuration space signals”) could have been easier and less confusing to handle. The tl_cfg_add, tl_cfg_ctl, tl_cfg_ctl_wr, tl_cfg_sts and tl_cfg_sts_wr are documented in a somewhat confusing manner, and it’s not always 100% clear what information is where.

And I haven’t even started with the PCI Express protocol itself. Not to mention the host driver, in particular if it’s for Windows. So indeed, Xillybus is good news.

For more information, please contact a Sopto representative by calling 86-755-36946668, or by sending an email to info@sopto.com